Twin Builder: Active Filter와 등가 전달 함수

김인섭 | 2026년 03월 11일본 사례에서는 Operational Amplifier 해석과 그와 동일한 전달함수(Transfer function)을 보여줍니다.

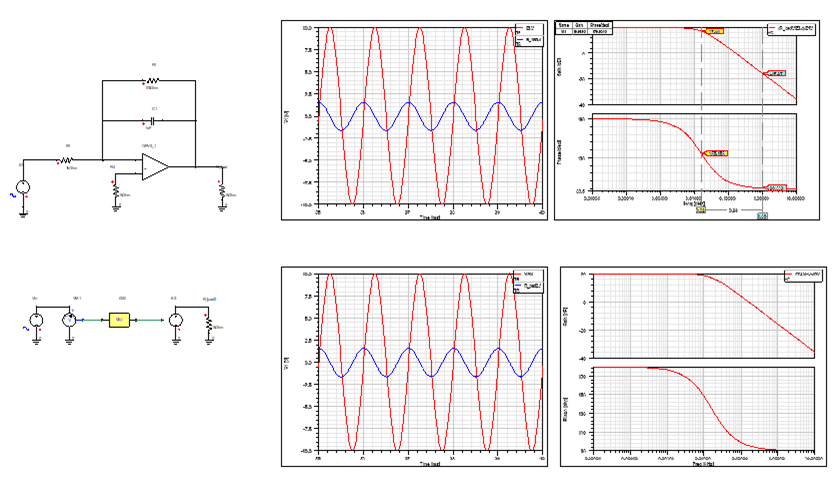

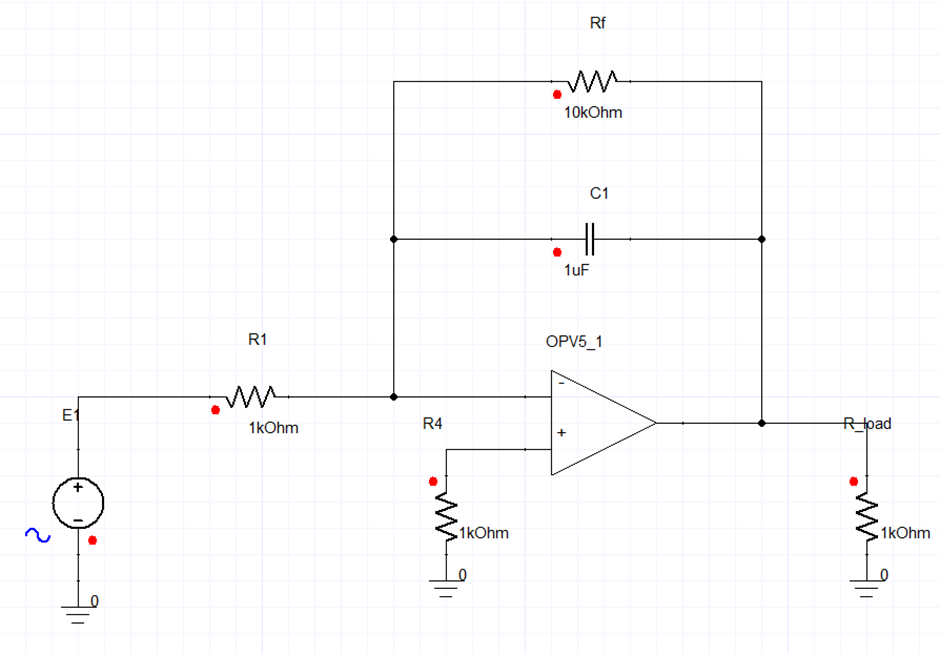

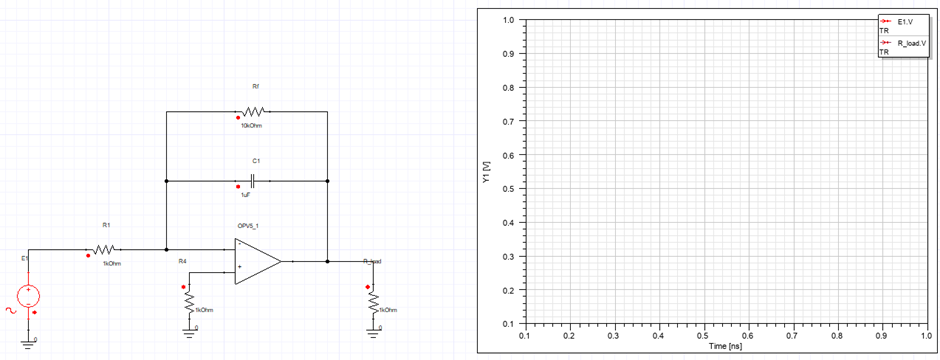

그림과 같이 회로도를 구성합니다.

(Amp 라이브러리 위치: Simplorer Elements→ Basic Elements→ Circuit→ Semiconductors Device Level → Operational Amplifier)

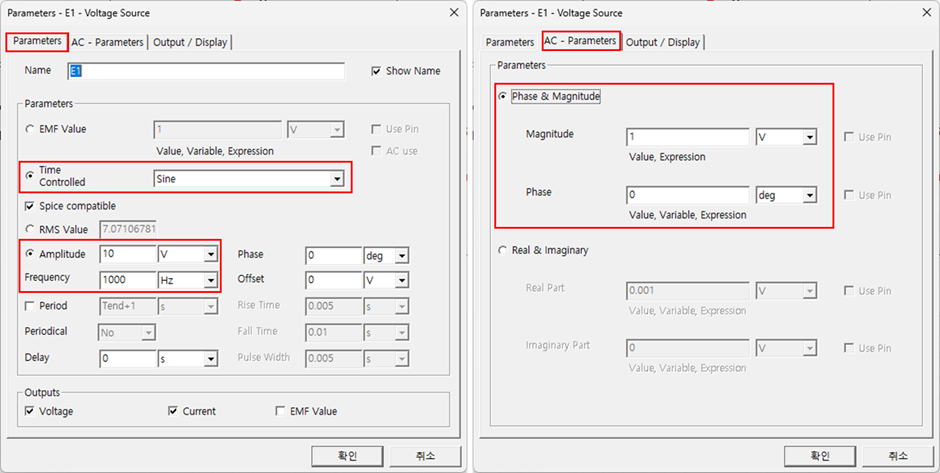

Voltage Source를 더블 클릭하고 the Parameters Tab을 선택한 후 다음과 같이 설정합니다.

• Time Controlled: Checked – Sine

• Amplitude: 10 V

• Frequency: 1000 Hz

AC-Parameters Tab을 클릭하여 다음과 같이 설정합니다.

• Phase and Magnitude: Checked

• Magnitude: 1 V

• Phase: 0 deg

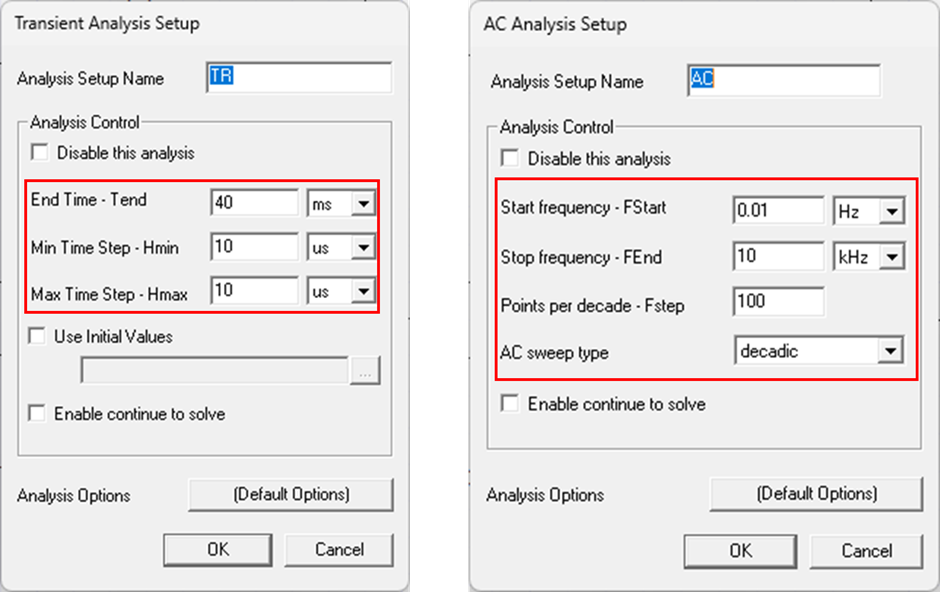

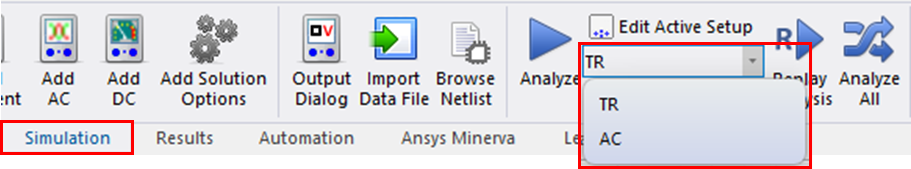

Transient 해석과 Ac해석을 모두 수행하기 위한 solver setup → 시간에 따른 결과(TR) / Bode plot(AC)을 다음과 같이 진행합니다.

TR setup

• Tend: 40 ms

• Hmin: 10 us

• Hmax: 10 us

AC setup (Simplorer Circuit → Solution setup → Add AC…)

• Start Frequency - FStart: 0.01 Hz

• Stop Frequency - FEnd: 10 kHz

• Points per decade - FStep: 100

• AC sweep type: Decadic

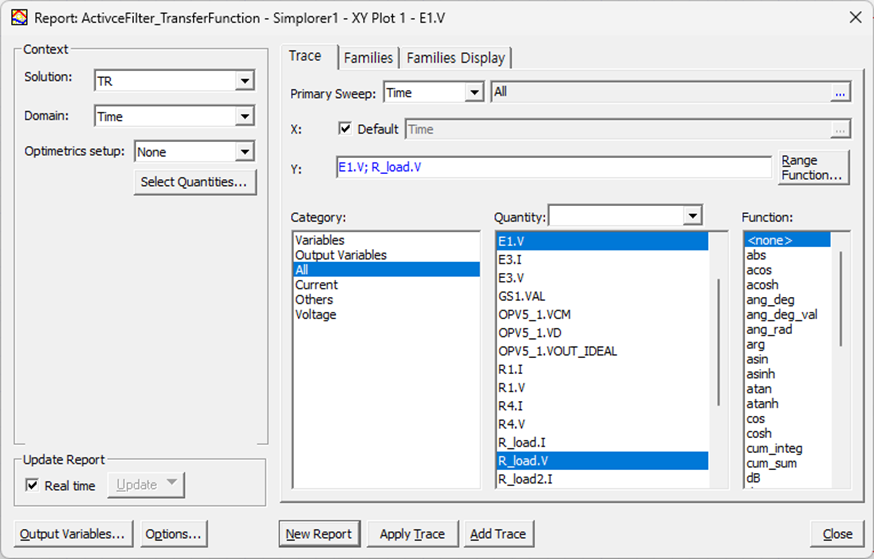

Draw→ Report→ Rectangular Plot 선택합니다.

입력전압원 E1의 전압강하량과 출력저항 R_load의 전압강하량 (E1.V and R_load.V)

Click ‘New Report’ → Schemetic에 Plot data를 Drag&Drop합니다.

Simplorer Circuit→ Analyze → Run the Simulation (TR)로 시간 해석 진행

Toolbar 에서 Solver type을 AC로 변경 → Run the simulation again

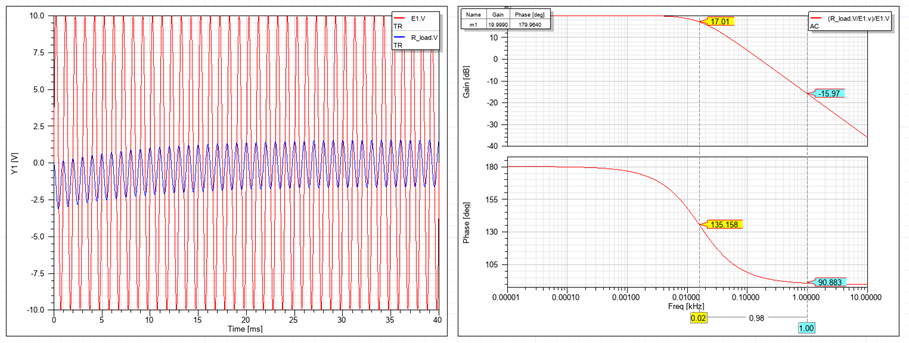

두가지 형태의 결과 확인 가능 ( Transient / Bode plot )

등가 전달함수 생성

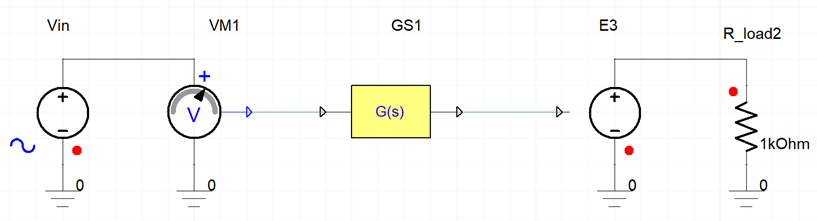

하기의 그림처럼 회로 결선합니다. (GS1 block은 Active filter특성, Vin은 Filter의 입력 신호, VM1은 Vin의 Conservative한 신호를 Non-Conservative한 신호로 출력, E3는 Non-conservative한 Gs1의 출력 신호를 Conservative한 신호로 출력, Vin을 앞서 설정한 E1과 동일하게 정의)

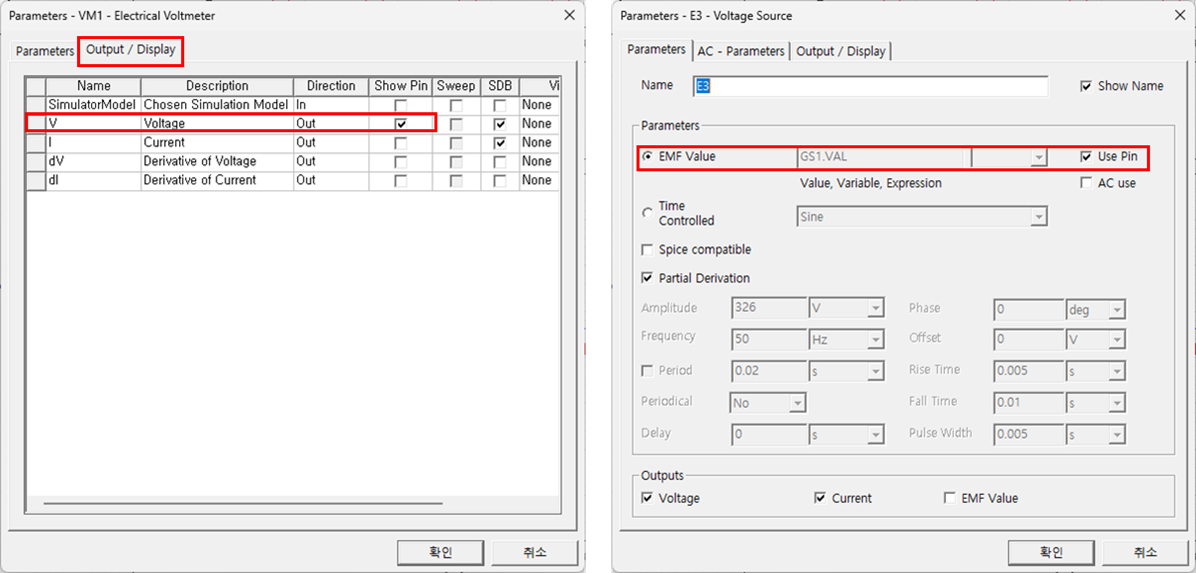

• VM1 Voltage미터 더블클릭 → “Output/Display” tab선택 → Voltage변수 V에 “Show Pin”

• E3 전압원 더블클릭 → EMF value를 Pin으로 받기 설정

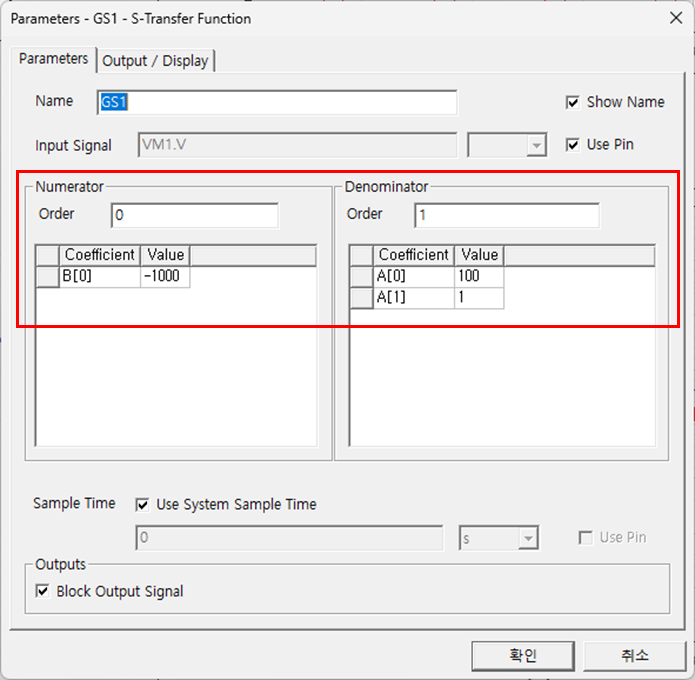

• Active filter의 극 주파수 “Fp ” = 15.9Hz → wp = 100 rad/s (크기=0), DC gain = 20dB (크기=10) → 전달함수 G(s) = 1000/(s + 100) (17dB = 7.08)

• Note -1000 은 filter의 반전 특성을 반영

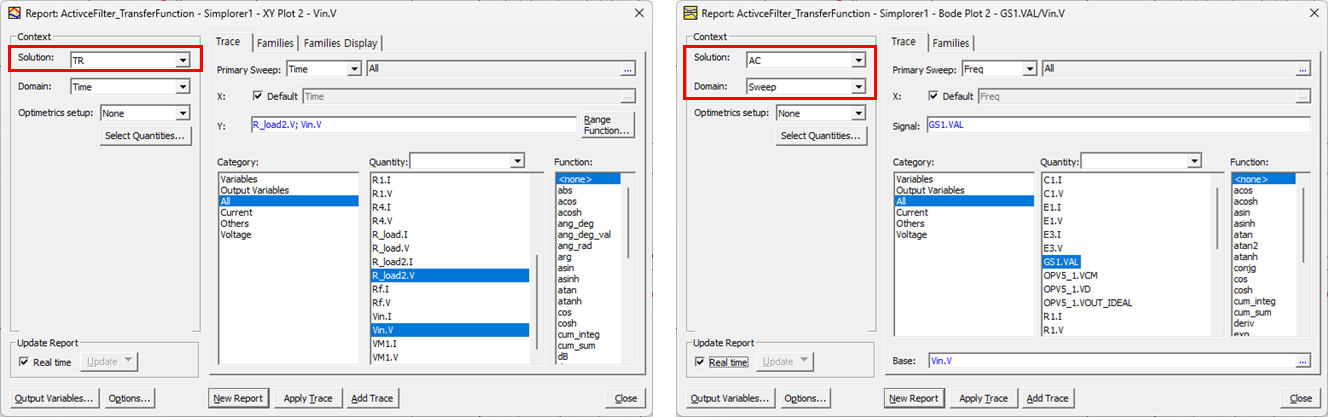

• Rectangular plot 에서 “TR” Solution 선택, 출력신호 Vin.V and R_load2.V

• Bode plot 추가, Base 신호로 Vin.V , 출력신호로 GS1.VAL

아래와 같이 두 특성이 동일함을 확인할 수 있습니다.