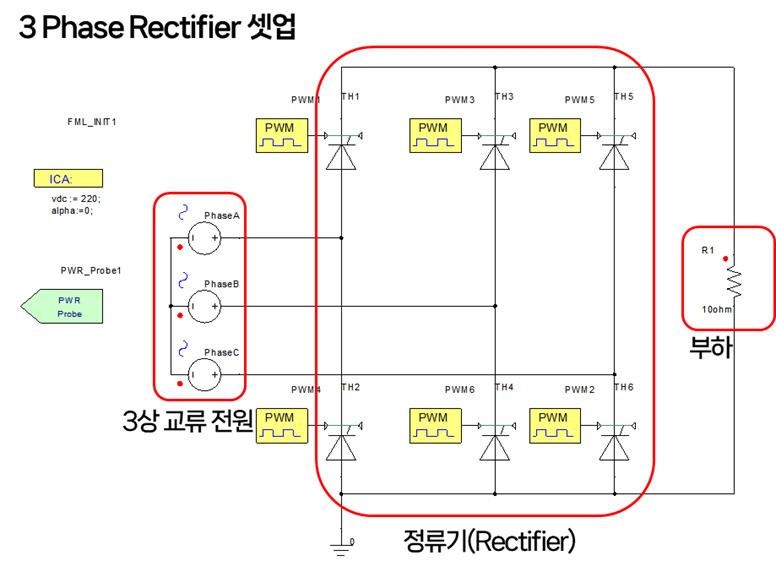

Twin Builder: 3-Phase Rectifier 해석 및 역률 개선

김인섭 | 2026년 02월 13일Twin builder를 이용한 3상(3phase) Rectifier 예제 입니다.

사이리스터(Thyristor)라는 반도체 소자를 사용하여 정류기를 구성합니다.

사이리스터는 제어단자인 Gate와 Anode, Cathode로 구성된 3단자 단반향 반도체 소자입니다.

Gate에 신호를 통해 도통(Turn on)이 되어 Anode에서 Cathode 방향으로 전류가 흐릅니다. 외부적으로 전류가 끊기거나 역전압이 걸릴 때 off가 됩니다.

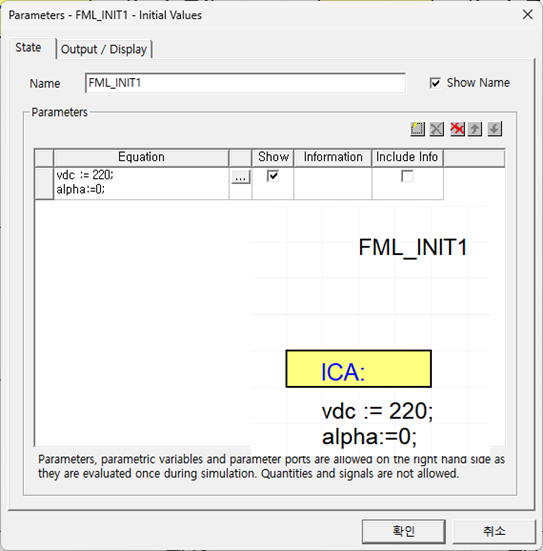

Variable Setting

DC link 전압과 도통각은 다음과 같으며 변수 설정을 통해 쉽게 변경할 수 있도록 설정했습니다.

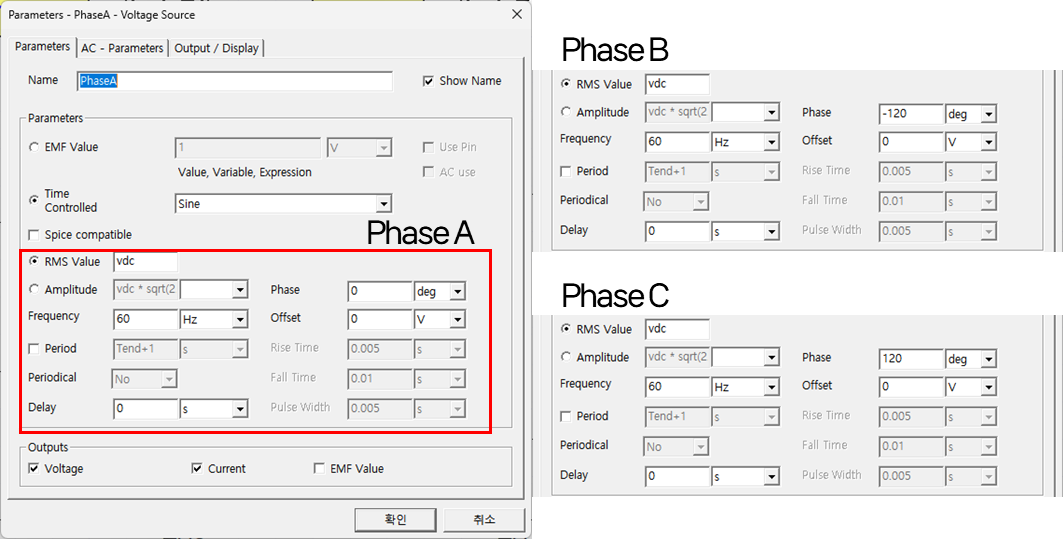

Voltage Source

A, B, C 상이 위상차를 120도씩 되도록 설정합니다. (A=0deg, B=-120deg, C=120deg)

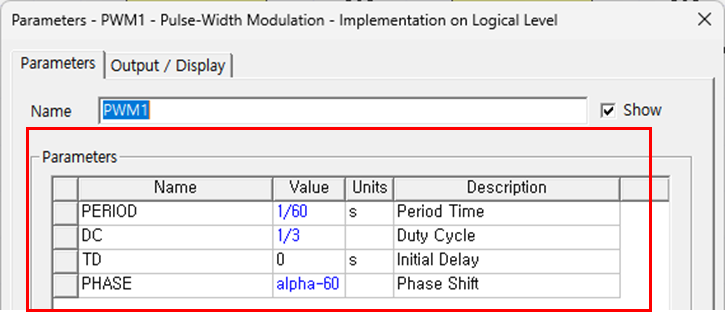

PWM

PERIOD는 1/60s(60Hz), DC는 1/3으로 설정한 후,

각 사이리스터에 연결된 PWM의 phase를 다음과 같이 설정합니다.

PWM1: Phase = alpha-60

PWM2: Phase = alpha-120

PWM3: Phase = alpha-180

PWM4: Phase = alpha-240

PWM5: Phase = alpha-300

PWM6: Phase = alpha

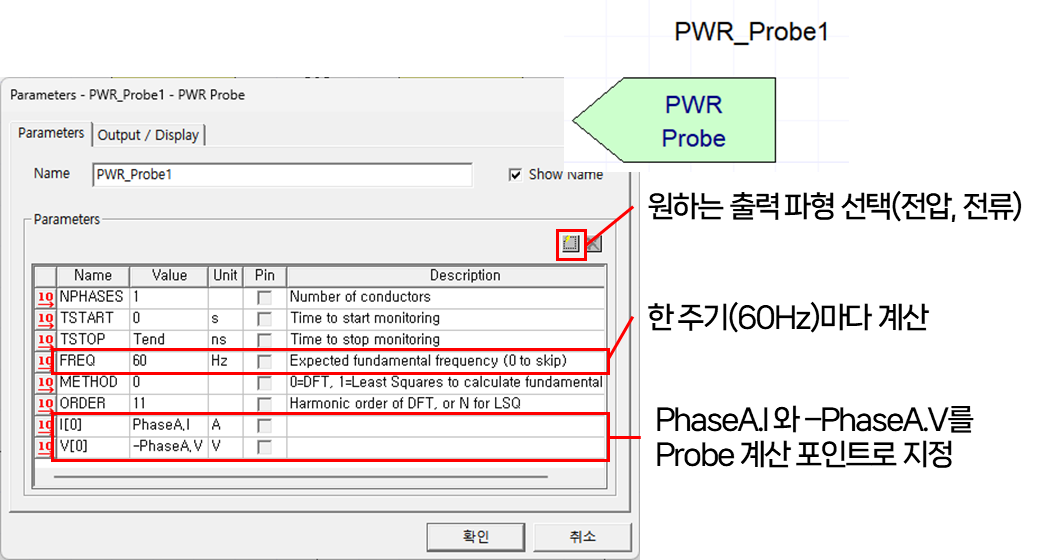

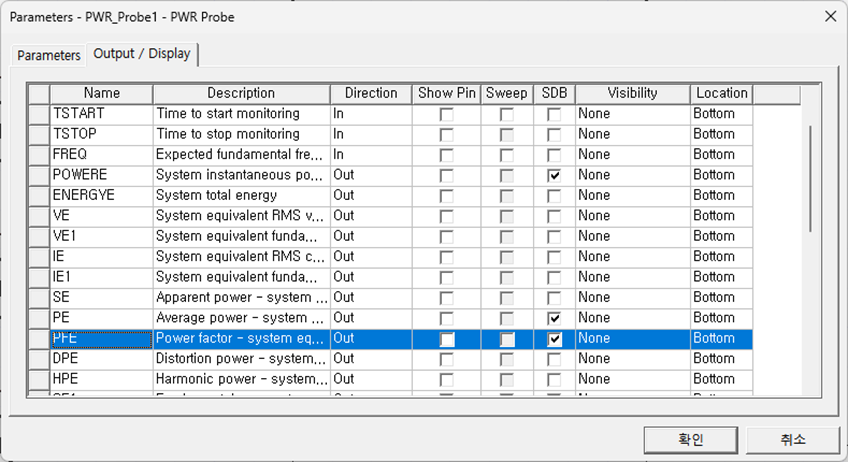

전력, 역률 등의 값을 분석하기 위해 전력 프로브를 추가하고 다음과 같이 설정합니다.

해석 후 결과로 plot 시킬 변수를 SDB 란에 check

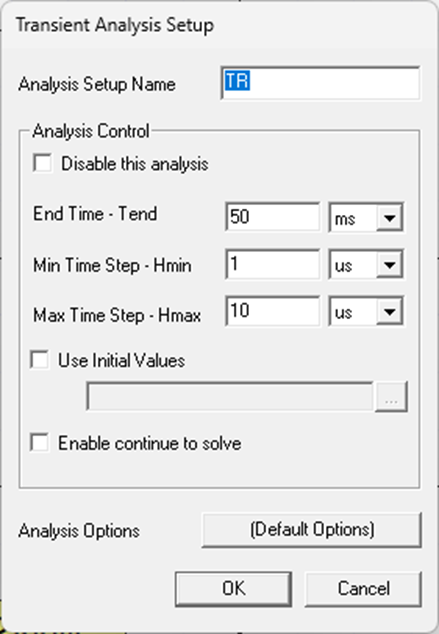

Analysis Setup

주파수 및 과도상태 시간 등을 고려하여 해석 시간 결정

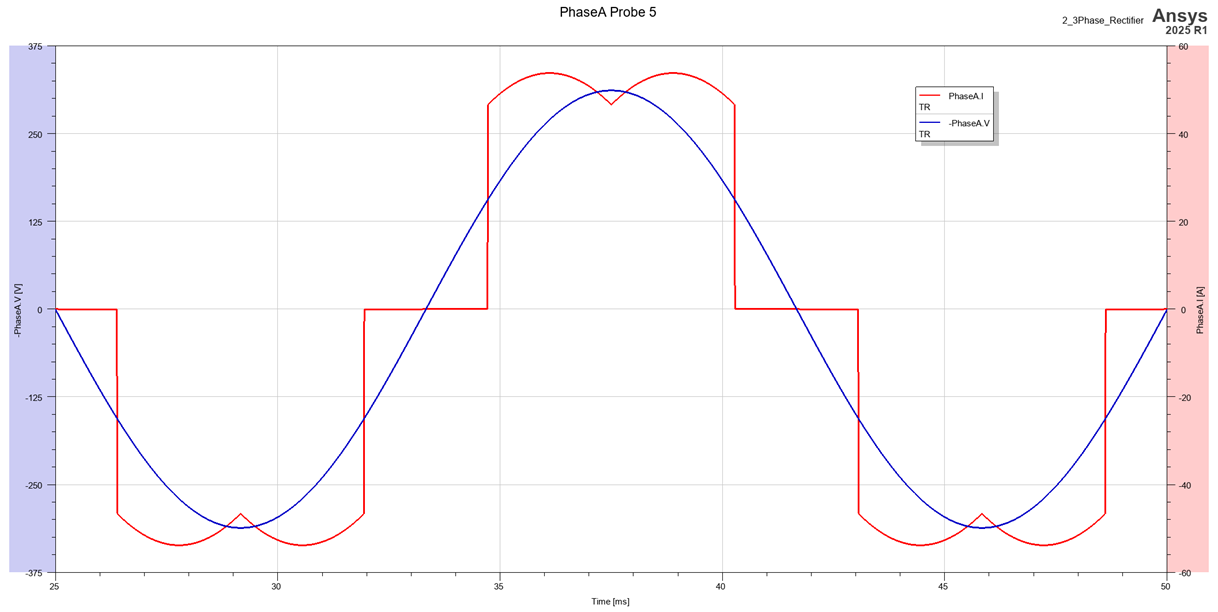

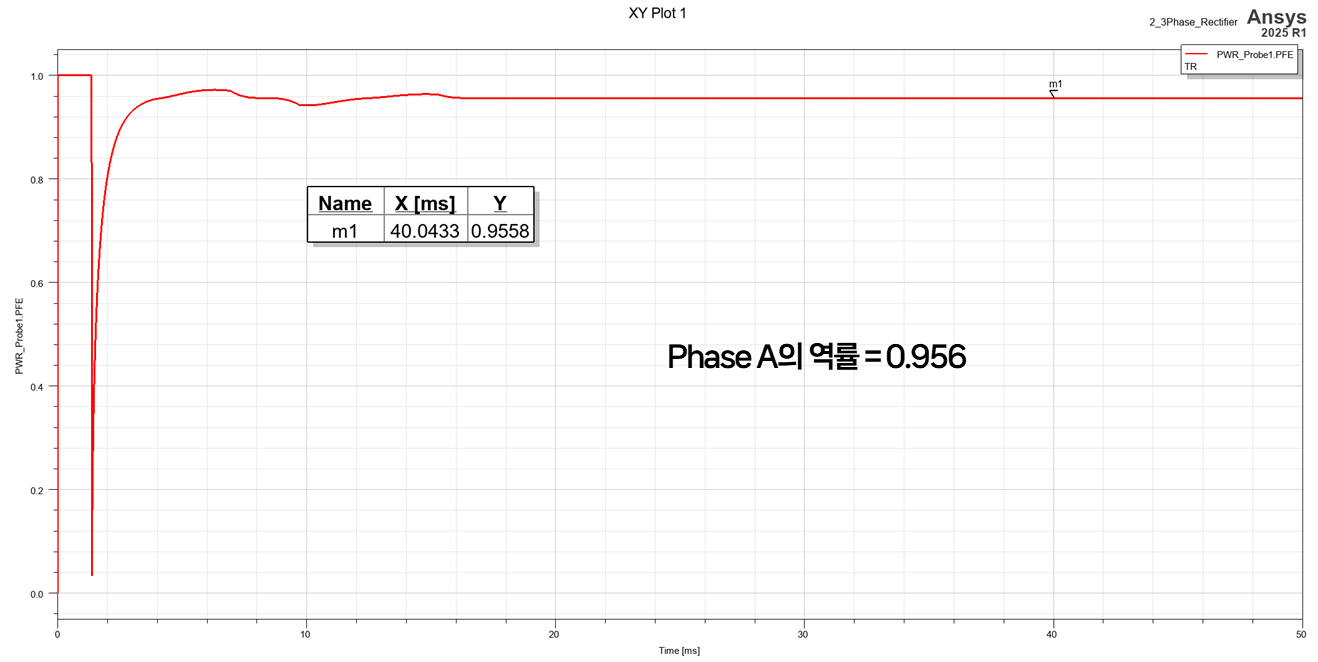

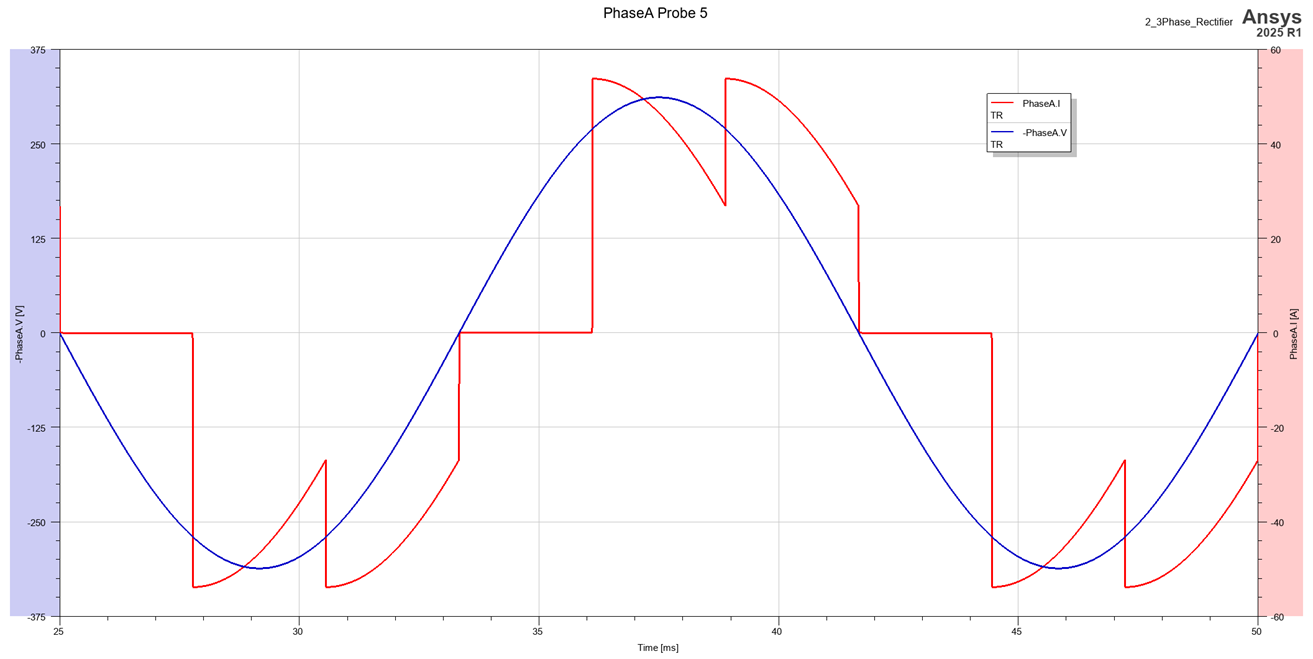

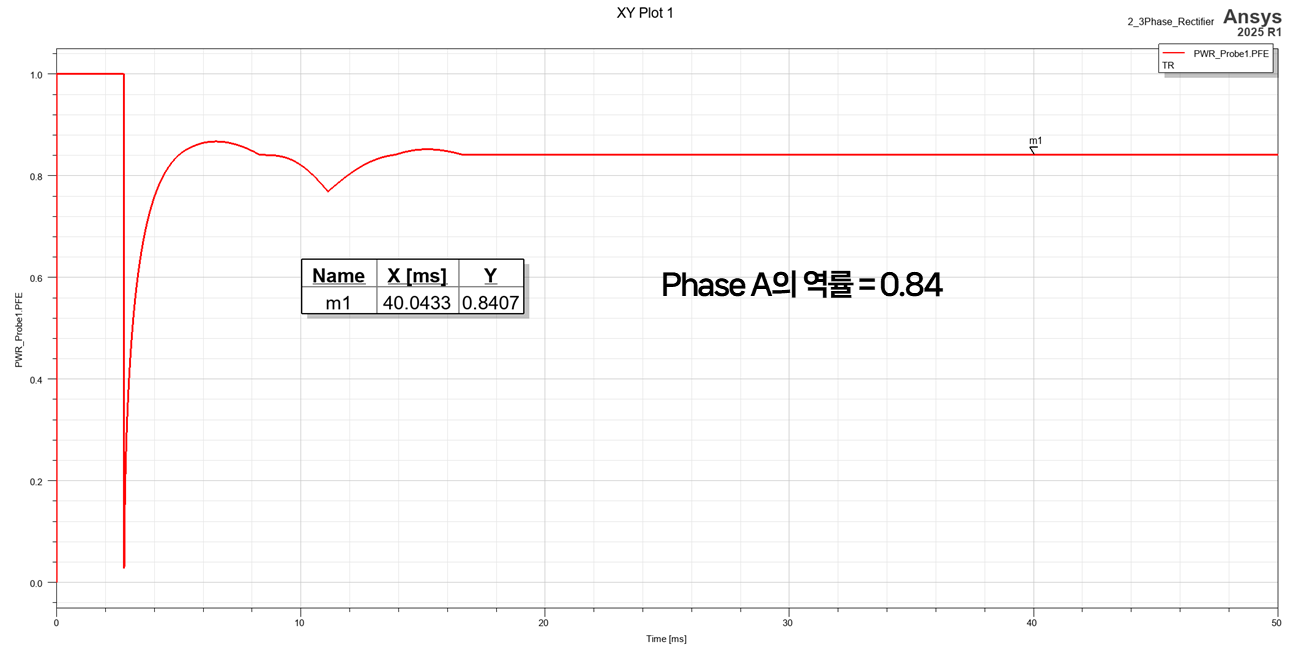

Results

부하에 전달되는 전력을 최대화 하기 위해 스위치의 on/off 신호의 위상을 30deg 앞당기면 (alpha =30) 역률이 개선됨을 알 수 있습니다.